The tables in the dropdowns below depict the external components connected to the MIO pins of the Eclypse Z7. For a complete and thorough description, refer to the Zynq Technical Reference manual. There are many aspects of the Zynq APSoC architecture that are beyond the scope of this document. Furthermore, cores implemented in the PL can trigger interrupts to the processors and perform DMA accesses to DDR3 memory. The programmable logic is also connected to the interconnect as a slave, and designs can implement multiple cores in the FPGA fabric that each also contain addressable control registers. The peripheral controllers are connected to the processors as slaves via the AMBA interconnect, and contain readable/writable control registers that are addressable in the processors’ memory space.

Peripheral controllers that do not have their inputs and outputs connected to MIO pins can instead route their I/O through the PL, via the Extended-MIO (EMIO) interface. The PS consists of many components, including the Application Processing Unit (APU, which includes 2 Cortex-A9 processors), Advanced Microcontroller Bus Architecture (AMBA) Interconnect, DDR3 Memory controller, and various peripheral controllers with their inputs and outputs multiplexed to 54 dedicated pins (called Multiplexed I/O, or MIO pins). The PL also does not contain the same configuration hardware as a typical 7-series FPGA, and it must be configured either directly by the processor or via the JTAG port. The PL is nearly identical to a Xilinx 7-series Artix FPGA, except that it contains several dedicated ports and buses that tightly couple it to the PS. Note that the PCIe Gen2 controller and Multi-gigabit transceivers are not available on the Zynq-7020 device. The figure below shows an overview of the Zynq APSoC architecture, with the PS colored light green and the PL in yellow. The Zynq APSoC is divided into two distinct subsystems: The Processing System (PS) and the Programmable Logic (PL).

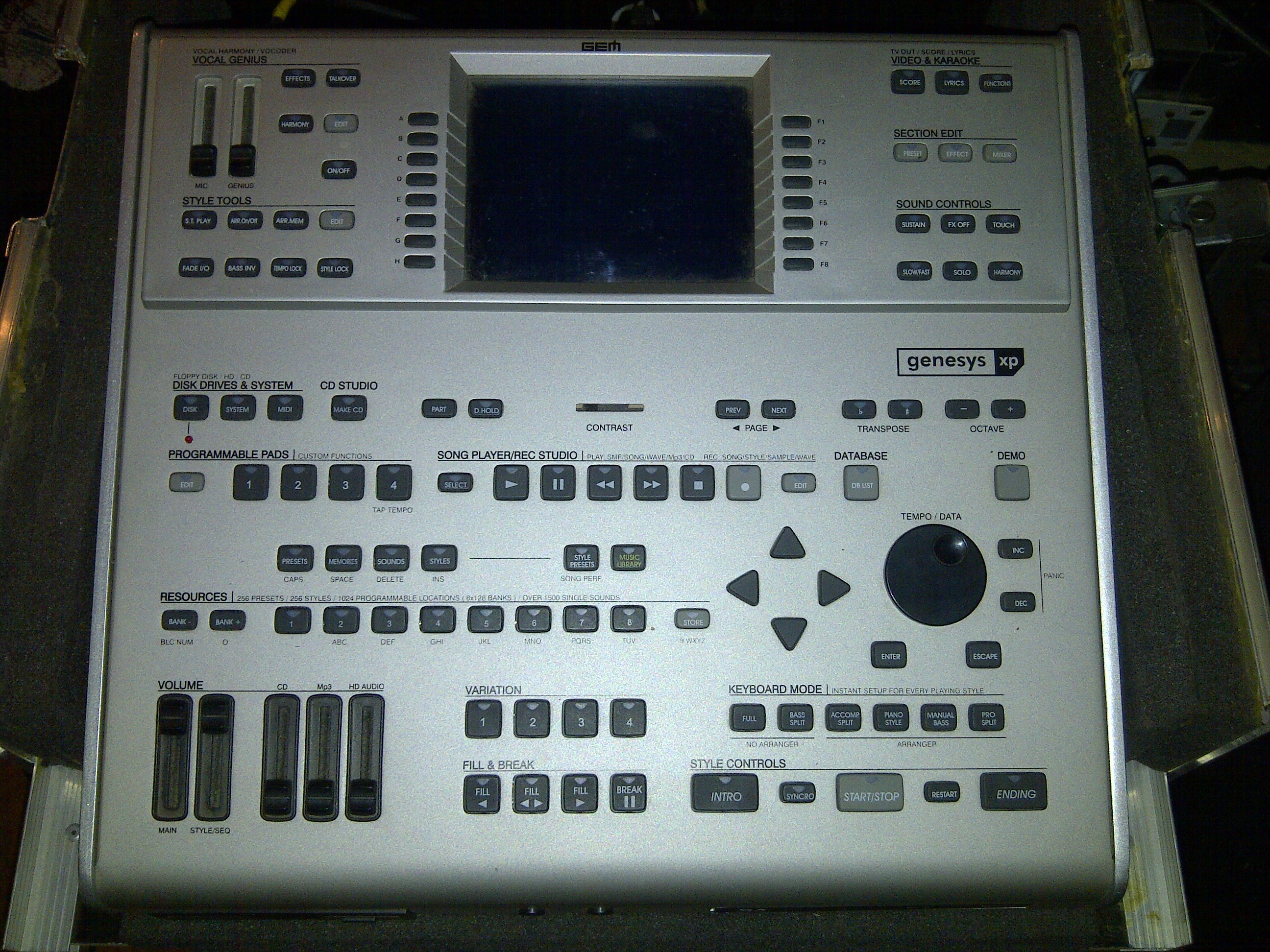

#GEM GENESYS PRO TUTORIALS SOFTWARE#

The Logic Analyzer assists with debugging logic that is running in hardware, and the HLS tool allows C code to be directly compiled into HDL.ĭigilent currently does not provide hardware platforms or examples for Xilinx's Vitis Unified Software Platform, however Vitis support is planned for the near future.ĭesign resources, example projects, and tutorials are available for download at the Eclypse Z7 Resource Center.

#GEM GENESYS PRO TUTORIALS FREE#

The Eclypse Z7 is supported under Vivado's free WebPACK™ license, which means the software is completely free to use, including the Logic Analyzer and High-level Synthesis (HLS) features. It is also possible to treat the Zynq AP SoC as a standalone FPGA for those not interested in using the processor in their design. It can be used for designing systems of any complexity, from a complete operating system running multiple server applications, down to a simple bare-metal program that controls some LEDs. This tool set melds FPGA logic design and embedded ARM software development into an easy to use, intuitive design flow. The Eclypse Z7 is fully compatible with Xilinx’s high-performance Vivado ® Design Suite. Digilent provides software examples targeting custom Petalinux projects, including support for each Digilent Zmod for high-speed I/O capabilities. Zynq platforms are well-suited to be embedded Linux targets, and the Eclypse Z7 is no exception. Digilent offers fully open and customizable hardware designs, Linux images, and Linux software applications. The software supports a variety of common programming languages, including Python, C/C++, and more. This system allows new users to get started without touching hardware until desired. Pre-built Linux images are accompanied by a software API for bulk data transfer. As a host board for Zmods, applications for the Eclypse can vary significantly between system configurations. It is a platform for research and rapid prototyping of test and measurement applications, potentially including software defined radio, ultrasound, other medical devices, and much more. A SYZYGY™ 1) compatible carrier board, it features two SYZYGY™ interface connectors, enabling high speed modular systems.Įclypse is designed to enable high speed analog data capture and analysis right out of the box. The Eclypse Z7 is a powerful prototyping platform, featuring Xilinx's Zynq-7000 APSoC.

0 kommentar(er)

0 kommentar(er)